Scratchpad memory

Scratchpad memory (SPRAM) is a high-speed internal memory directly connected to the CPU core and used for temporary storage to hold very small items of data for rapid retrieval. Scratchpads are employed for simplification of caching logic and to guarantee a unit can work without main memory contention in a system employing multiple cores, especially in embedded MCSoC systems. They are suited to storing temporary results.

While a cache memory uses a complex hardware controller to decide which data to keep in cache memories (L1 or L2) and which data to prefetch, the SPRAM approach does not require any hardware support in addition to the memory itself, but requires software to take control of all data transfers to and from Scratchpad memories. It is therefore the responsibility of the programmer to identify data sections that should be placed in SPRAM or place code in the program to appropriately move data from on-chip memory to SPRAM. For this reason, SPRAMs are sometimes called “software controlled caches”. Figure 3.20 illustrates the memory subsystem architecture with two SPRAMs (levels 1 and 2).

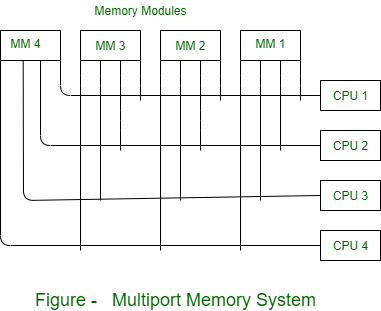

Multiport Memory System employs separate buses between each memory module and each CPU. A processor bus comprises the address, data and control lines necessary to communicate with memory. Each memory module connects each processor bus. At any given time, the memory module should have internal control logic to obtain which port can have access to memory.

Memory module can be said to have four ports and each port accommodates one of the buses. Assigning fixed priorities to each memory port resolve the memory access conflicts. the priority is established for memory access associated with each processor by the physical port position that its bus occupies in each module. Therefore CPU 1 can have priority over CPU 2, CPU 2 can have priority over CPU 3 and CPU 4 can have the lowest priority.

Advantage:-

High transfer rate can be achieved because of multiple paths

Disadvantage:-

- It requires expensive memory control logic and a large number of cables and connectors.

- It is only good for systems with small number of processors.

Tirthankar Pal

MBA from IIT Kharagpur with GATE, GMAT, IIT Kharagpur Written Test, and Interview

2 year PGDM (E-Business) from Welingkar, Mumbai

4 years of Bachelor of Science (Hons) in Computer Science from the National Institute of Electronics and Information Technology

Google and Hubspot Certification

Brain Bench Certification in C++, VC++, Data Structure and Project Management

10 years of Experience in Software Development out of that 6 years 8 months in Wipro

Selected in Six World Class UK Universities:-

King's College London, Durham University, University of Exeter, University of Sheffield, University of Newcastle, University of Leeds

No comments:

Post a Comment